# DAQScope<sup>™</sup> 5102 User Manual

Digitizing Oscilloscope for the PC

March 1997 Edition Part Number 321390A-01

$\odot$  Copyright 1997 National Instruments Corporation. All Rights Reserved.

### **Internet Support**

support@natinst.com

E-mail: info@natinst.com

FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

### **Bulletin Board Support**

BBS United States: (512) 794-5422 BBS United Kingdom: 01635 551422

BBS France: 01 48 65 15 59

**Fax-on-Demand Support**

(512) 418-1111

Telephone Support (U.S.)

Tel: (512) 795-8248 Fax: (512) 794-5678

### **International Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 527 2321, France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 5734815, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, U.K. 01635 523545

### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 Tel: (512) 794-0100

# **Important Information**

### Warranty

The DAQScope 5102 is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

### **Trademarks**

LabVIEW®, NI-DAQ®, RTSI®, ComponentWorks<sup>TM</sup>, CVI<sup>TM</sup>, DAQCard<sup>TM</sup>, DAQScope<sup>TM</sup>, Measure<sup>TM</sup>, MITE<sup>TM</sup>, and SCXI<sup>TM</sup> are trademarks of National Instruments Corporation.

Product and company names listed are trademarks or trade names of their respective companies.

#### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

Table of Contents

| JUOQA  | inis wanuai                                  |

|--------|----------------------------------------------|

|        | Organization of This Manualix                |

|        | Conventions Used in This Manualx             |

|        | National Instruments Documentationxi         |

|        | Customer Communicationxi                     |

| Chapte | er 1                                         |

| Introd | uction                                       |

|        | About Your DAQScope 51021-1                  |

|        | What You Need to Get Started                 |

|        | Software Programming Choices                 |

|        | National Instruments Application Software1-3 |

|        | NI-DAQ Driver Software1-4                    |

|        | Optional Equipment                           |

|        | Unpacking                                    |

|        | ation and Configuration  Installation        |

| Chapte | er 3                                         |

| -      | er Basics                                    |

|        | Understanding Digitizers                     |

|        | Nyquist Theorem3-1                           |

|        | Analog Bandwidth3-2                          |

|        | Sample Rate                                  |

|        | Vertical Sensitivity                         |

|        | ADC Resolution                               |

|        | Record Length                                |

|        | Triggering Options                           |

|        | Making Accurate Measurements                 |

| Understanding the Probe and Its Effects on Your Waveform | 3-9  |

|----------------------------------------------------------|------|

| The Passive Probe                                        |      |

| How to Compensate Your Probe                             |      |

| Active and Current Probes                                |      |

| Chapter 4                                                |      |

| Hardware Overview                                        |      |

| I/O Connector                                            | 4-2  |

| Signal Connections                                       | 4-3  |

| Analog Input                                             |      |

| ADC Pipeline Delay                                       |      |

| Acquisition Modes                                        |      |

| Posttrigger Acquisition                                  |      |

| Pretrigger Acquisition                                   |      |

| Trigger Sources                                          |      |

| Analog Trigger Circuit                                   |      |

| Trigger Hold-Off                                         |      |

| Random Interleaved Sampling                              |      |

| Calibration                                              | 4-20 |

| RTSI Bus Trigger and Clock Lines                         | 4-20 |

| PFI Lines                                                | 4-22 |

| PFI Lines as Inputs                                      | 4-22 |

| PFI Lines as Outputs                                     | 4-22 |

| Master/Slave Operation                                   | 4-24 |

| Restrictions                                             |      |

| Connecting Devices                                       | 4-24 |

| Determining Pretriggered and Posttriggered Scan Counts   |      |

| Other Considerations                                     |      |

|                                                          |      |

# Appendix A Specifications

Appendix B

PC Card Questions and Answers

Appendix C

Customer Communication

# Glossary

### Index

# **Figures**

| Figure 1-1.  | The Relationship between the Programming Environment,        |      |

|--------------|--------------------------------------------------------------|------|

|              | NI-DAQ, and Your Hardware                                    | 1-5  |

| Figure 3-1.  | Sine Wave Demonstrating the Nyquist Frequency                | 3-1  |

| Figure 3-2.  | Analog Bandwidth                                             | 3-2  |

| Figure 3-3.  | 1 MHz Sine Wave Sample                                       |      |

| Figure 3-4.  | Transfer Function of a 3-Bit ADC                             | 3-4  |

| Figure 3-5.  | Dynamic Range of an 8-Bit ADC with Three Different           |      |

|              | Gain Settings                                                | 3-6  |

| Figure 3-6.  | Difficult Pulse Train Signal                                 | 3-8  |

| Figure 3-7.  | Typical 10X Probe                                            | 3-9  |

| Figure 3-8.  | Connecting the Probe Compensation Cabling                    | 3-11 |

| Figure 3-9.  | Probe Compensation Comparison                                | 3-11 |

| Figure 4-1.  | DAQScope 5102 Block Diagram                                  | 4-1  |

| Figure 4-2.  | AT-5102 and PCI-5102 Connectors                              | 4-2  |

| Figure 4-3.  | DAQCard-5102 Connector                                       | 4-3  |

| Figure 4-4.  | Scan Clock Delay                                             | 4-5  |

| Figure 4-5.  | Posttrigger Acquisition                                      | 4-7  |

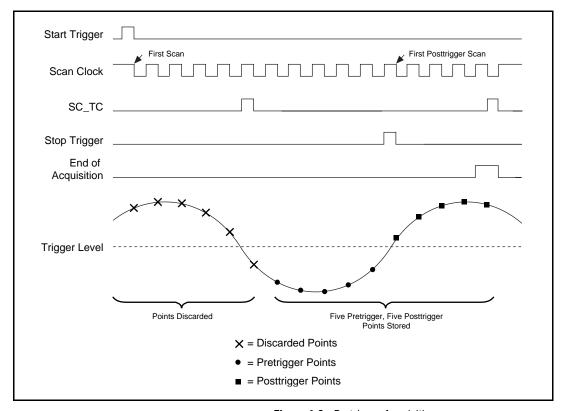

| Figure 4-6.  | Pretrigger Acquisition                                       | 4-10 |

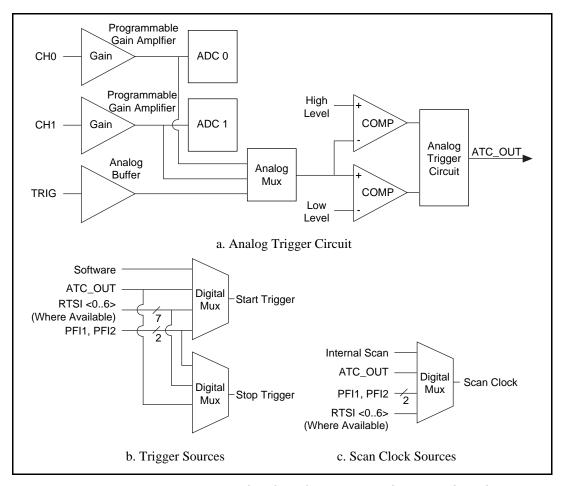

| Figure 4-7.  | Scan Clock, Start Trigger, and Stop Trigger Signal Sources   | 4-12 |

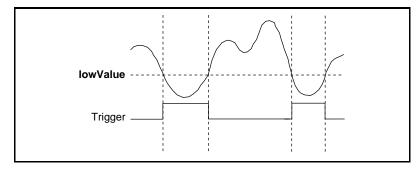

| Figure 4-8.  | Below-Low-Level Analog Triggering Mode                       | 4-13 |

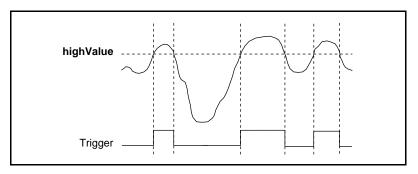

| Figure 4-9.  | Above-High-Level Analog Triggering Mode                      | 4-13 |

| Figure 4-10. | Inside-Region Analog Triggering Mode                         | 4-14 |

| Figure 4-11. | High-Hysteresis Analog Triggering Mode                       | 4-14 |

| Figure 4-12. | Low-Hysteresis Analog Triggering Mode                        | 4-15 |

| Figure 4-13. | Pretrigger and Posttrigger Acquisitions with Hold-Off        | 4-16 |

| Figure 4-14. | Waveform Reconstruction with RIS                             | 4-18 |

| Figure 4-15. | Relationship between Interpolation Factor, Logical Bins, and |      |

|              | Physical Bins                                                | 4-19 |

| Figure 4-16. | RTSI Bus Trigger Lines                                       | 4-21 |

| Figure 4-17. | Retriggered Acquisition Programming Flowchart                | 4-27 |

### **Tables**

| Table 4-1. | I/O Connector Signal Descriptions                  | 4-3  |

|------------|----------------------------------------------------|------|

| Table 4-2. | CH0 and CH1 Input Ranges                           | 4-4  |

| Table 4-3. | AC/DC Coupling Change Settling Rates               | 4-5  |

| Table 4-4. | Possible Number of Samples for Posttriggered Scans | 4-6  |

| Table 4-5. | Posttrigger Acquisition Signals                    | 4-8  |

| Table 4-6. | Possible Number of Samples for Pretriggered Scans  | 4-9  |

| Table 4-7. | Pretrigger Acquisition Signals                     | 4-11 |

| Table 4-8. | Master/Slave Programming                           | 4-26 |

About This Manual

This manual describes the mechanical and electrical aspects of the DAQScope 5102 and contains information concerning their installation and operation. The DAQScope PCI-5102, DAQScope AT-5102, and DAQScope DAQCard-5102 devices are analog input devices that combine benefits of digitizers and oscilloscopes.

# **Organization of This Manual**

The DAQScope 5102 User Manual is organized as follows:

- Chapter 1, Introduction, describes the DAQScope 5102, lists the

optional software and optional equipment, and explains how to

unpack your DAQScope 5102.

- Chapter 2, *Installation and Configuration*, describes how to install and configure your DAQScope 5102.

- Chapter 3, *Digitizer Basics*, explains basic information you need to understand about making measurements with digitizers, including important terminology and using your probe.

- Chapter 4, Hardware Overview, includes an overview of the DAQScope 5102, explains the operation of each functional unit making up your DAQScope 5102, and describes the signal connections.

- Appendix A, *Specifications*, lists the specifications of the DAQScope 5102.

- Appendix B, PC Card Questions and Answers, contains a list of common questions and answers relating to PC Card (PCMCIA) operation.

- Appendix C, *Customer Communication*, contains forms you can use to request help from National Instruments or to comment on our products and manuals.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, and symbols.

• The *Index* contains an alphabetical list of key terms and topics in this manual, including the page where you can find each one.

### **Conventions Used in This Manual**

The following conventions are used in this manual:

5102 device 5102 device refers to one of the DAQScope 5102 Series of devices.

bold Bold text denotes menus, menu items, or dialog box buttons or options.

**bold italic** Bold italic text denotes a note, caution, or warning.

DAQScope 5102 DAQScope 5102 is a generic term that denotes one or more of the

PCI-5102, AT-5102, and DAQCard-5102 devices.

digitizer Digitizer refers to a 5102 device.

italic Italic text denotes emphasis, a cross reference, or an introduction to a

key concept.

NI-DAQ NI-DAQ refers to the NI-DAQ software for PC compatibles or

Macintosh unless otherwise noted.

Plug and Play Plug and Play refers to a device that is fully compatible with the

industry standard Plug and Play specification. Plug and Play systems automatically arbitrate and assign system resources, freeing the user from manually configuring jumpers or switches to configure settings

such as the product's base address and interrupt level.

Abbreviations, acronyms, metric prefixes, mnemonics, symbols, and

terms are listed in the Glossary.

### **National Instruments Documentation**

The DAQScope 5102 User Manual is one piece of the documentation set for your data acquisition (DAQ) system. You could have any of several types of manuals, depending on the hardware and software in your system. Use the manuals you have as follows:

- Your DAQ hardware user manuals—These manuals have detailed information about the DAQ hardware that plugs into or is connected to your computer. Use these manuals for hardware installation and configuration instructions, specification information about your DAQ hardware, and application hints.

- Software documentation—You may have both application software and NI-DAQ software documentation. National Instruments application software includes LabVIEW, LabWindows®/CVI, ComponentWorks, Measure, and VirtualBench. After you set up your hardware system, use the application software documentation to help you write your application. If you have a large and complicated system, it is worthwhile to look through the software documentation before you configure your system.

- Accessory manuals—If you are using accessory products, read the terminal block and cable assembly installation guides. They explain how to physically connect the relevant pieces of the system. Consult these guides when you are making your connections.

### **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix C, *Customer Communication*.

Introduction

This chapter describes the DAQScope 5102, lists the optional software and optional equipment, and explains how to unpack your DAQScope 5102.

## **About Your DAQScope 5102**

Thank you for your purchase of a National Instruments DAQScope 5102 Series device. The DAQScope 5102 Series consists of three different devices for your choice of bus: the PCI version for the PCI bus, the AT version for the ISA bus, and the DAQCard version for the PCMCIA slot. Your 5102 device has the following features:

- Two 8-bit resolution analog input channels

- Sampling rate of 1 kS/s to 20 MS/s real-time sampling; 1 GS/s random interleaved sampling (RIS)

- 15 MHz analog input bandwidth

- Analog trigger channel with software-selectable level, slope, and hysteresis

- Two digital triggers

- Software-selectable AC/DC coupling

- 663,000-sample onboard memory

- Real-Time System Integration (RTSI) triggers (PCI-5102 and AT-5102 only)

All 5102 devices follow industry-standard Plug and Play specifications on all platforms and offer seamless integration with compliant systems. If your application requires more than two channels for data acquisition, you can synchronize multiple devices on all platforms using RTSI bus triggers on devices that use the RTSI bus or the digital triggers on the I/O connector.

To improve timing resolution for repetitive signals, you can use RIS on your DAQScope 5102. This method of sampling allows you to view pretrigger data and achieve an effective sampling rate as high as 1 GS/s, 50 times the real-time sampling rate on the device.

Detailed specifications of the DAQScope 5102 devices are in Appendix A, *Specifications*.

### What You Need to Get Started

| 10 | set up and use your DAQScope 5102, you will need the followin           |  |  |

|----|-------------------------------------------------------------------------|--|--|

|    | One of the following DAQScope 5102 devices:                             |  |  |

|    | – PCI-5102                                                              |  |  |

|    | – AT-5102                                                               |  |  |

|    | - DAQCard-5102                                                          |  |  |

|    | DAQScope 5102 User Manual                                               |  |  |

|    | NI-DAQ for PC compatibles, version 5.0 or later                         |  |  |

|    | One of the following software packages and documentation:               |  |  |

|    | – LabVIEW                                                               |  |  |

|    | <ul><li>LabWindows/CVI</li></ul>                                        |  |  |

|    | - Measure                                                               |  |  |

|    | - VirtualBench-Scope                                                    |  |  |

|    | - ComponentWorks                                                        |  |  |

|    | Cables and accessories                                                  |  |  |

|    | - Two SP200B 10X-1X selectable oscilloscope probes                      |  |  |

|    | <ul> <li>SMB100 cable and screwdriver for probe compensation</li> </ul> |  |  |

|    | <ul> <li>PSH32-C5 I/O cable assembly (DAQCard-5102 only)</li> </ul>     |  |  |

|    | Vinyl pouch for storing cables and accessories                          |  |  |

|    | Your computer                                                           |  |  |

|    |                                                                         |  |  |

# **Software Programming Choices**

There are several options to choose from when programming your National Instruments DAQ hardware. You can use LabVIEW, LabWindows/CVI, ComponentWorks, Measure, or VirtualBench.

### **National Instruments Application Software**

LabVIEW and LabWindows/CVI are innovative program development software packages for data acquisition and control applications. LabVIEW uses graphical programming, whereas LabWindows/CVI enhances traditional programming languages. Both packages include extensive libraries for data acquisition, instrument control, data analysis, and graphical data presentation.

LabVIEW features interactive graphics, a state-of-the-art user interface, and a powerful graphical programming language. The LabVIEW Data Acquisition VI Library, a series of VIs for using LabVIEW with National Instruments DAQ hardware, is included with LabVIEW.

LabWindows/CVI features interactive graphics, a state-of-the-art user interface, and uses the ANSI standard C programming language. The LabWindows/CVI Data Acquisition Library, a series of functions for using LabWindows/CVI with National Instruments DAQ hardware, is included with the NI-DAQ software kit.

# Note: DAQScope 5102 devices can use only the Easy I/O interface in LabWindows/CVI.

Using LabVIEW or LabWindows/CVI software will greatly reduce the development time for your data acquisition and control application.

VirtualBench is a suite of VIs that allows you to use your data acquisition products just as you use stand-alone instruments, but you benefit from the processing, display, and storage capabilities of PCs. VirtualBench instruments load and save waveform data to disk in the same forms used in popular spreadsheet programs and word processors. A report generation capability complements the raw data storage by adding timestamps, measurements, user name, and comments.

The complete VirtualBench suite contains VirtualBench-Scope, VirtualBench-DSA, VirtualBench-Function Generator, VirtualBench-FG, VirtualBench-Arb, VirtualBench-AODC,

VirtualBench-DIO, VirtualBench-Board Calibrator, VirtualBench-DMM, and VirtualBench-Logger. Your DAQScope 5102 kit contains a copy of VirtualBench-Scope. VirtualBench-Scope is a turn-key application you can use to make measurements as you would with a standard oscilloscope.

ComponentWorks contains tools for data acquisition and instrument control built on NI-DAQ driver software. ComponentWorks provides a higher-level programming interface for building virtual instruments with Visual Basic, Visual C++, Borland Delphi, and Microsoft Internet Explorer. With ComponentWorks, you can use all of the configuration tools, resource management utilities, and interactive control utilities included with NI-DAQ.

Measure is a data acquisition and instrument control add-in for Microsoft Excel. With Measure, you can acquire data directly from plug-in DAQ boards, GPIB instruments, or serial (RS-232) devices. Measure has easy-to-use dialogs for configuring your measurements. Your data is placed directly into Excel worksheet cells, from which you can perform your analysis and report generation operations using the full power and flexibility of Excel.

### NI-DAQ Driver Software

The NI-DAQ driver software is included at no charge with all National Instruments DAQ hardware. NI-DAQ is not packaged with accessory products. NI-DAQ has an extensive library of functions that you can call from your application programming environment.

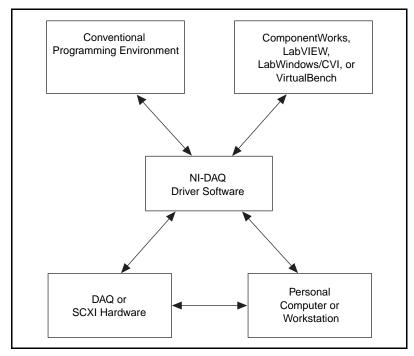

Whether you are using conventional programming languages, LabVIEW, LabWindows/CVI, VirtualBench, or ComponentWorks, your application uses the NI-DAQ driver software, as illustrated in Figure 1-1.

Figure 1-1. The Relationship between the Programming Environment, NI-DAQ, and Your Hardware

# **Optional Equipment**

National Instruments offers a variety of products to use with your DAQScope 5102, including probes, cables, and other accessories, as follows:

- TPI9258 100X probe with accessories for high-voltage applications

- SMB200 SMB male to SMB male cable for master/slave timing and triggering, 1 ft

- SMB300 SMB male to alligator clip cable for external triggering,

3 ft

- RTSI bus cables

For more specific information about these products, refer to your National Instruments catalogue or web site, or call the office nearest you.

## Unpacking

### ◆ PCI-5102 and AT-5102

Your device is shipped in an antistatic package to prevent electrostatic damage to the device. Electrostatic discharge can damage several components on the device. To avoid such damage in handling the device, take the following precautions:

- Ground yourself via a grounding strap or by holding a grounded object.

- Touch the antistatic package to a metal part of your computer chassis before removing the device from the package.

- Remove the device from the package and inspect the device for loose components or any other sign of damage. Notify National Instruments if the device appears damaged in any way. *Do not* install a damaged device into your computer.

- *Never* touch the exposed pins of connectors.

### ♦ DAQCard-5102

Your PC card is shipped in an antistatic vinyl case; when you are not using the card, you should store it in this case. Because the card is enclosed in a fully shielded case, no additional electrostatic precautions are necessary. However, for your own safety and to protect the card, never attempt to touch the pins of the connectors.

# Installation and Configuration

This chapter describes how to install and configure your DAQScope 5102.

### Installation

### Note:

You should install your driver software before installing your hardware. Refer to the DAQScope 5102 Read Me First for software installation information.

If you have an older version of NI-DAQ already in your system, that software will not work with your device. Install NI-DAQ from the CD shipped with your DAQScope 5102.

◆ PCI-5102 and DAQScope AT-5102

You can install the PCI-5102 in any PCI slot and the DAQScope AT-5102 in any ISA slot in your computer. However, for best noise performance, leave as much room as possible between the DAQScope 5102 and other hardware. Before installing your 5102 device, consult your PC user manual or technical reference manual for specific instructions and warnings. Follow these general instructions to install your DAQScope 5102:

- 1. Write down the DAQScope 5102 serial number on the *DAQScope 5102 Hardware and Software Configuration Form* in Appendix C. You may need this serial number for future reference if you need to contact technical support.

- 2. Turn off your computer.

- 3. Remove the top cover or access port to the I/O channel.

- 4. Remove the expansion slot cover on the back panel of the computer.

- 5. For the PCI-5102, insert the card into a PCI slot. For the AT-5102, insert the card into a 16-bit ISA slot. It may be a tight fit, but do not force the device into place.

- 6. Screw the mounting bracket of the DAQScope 5102 to the back panel rail of the computer.

- 7. Check the installation.

- 8. Replace the cover.

- 9. Plug in and turn on your computer.

The PCI-5102 or AT-5102 is now installed.

### ♦ DAQCard-5102

You can install the DAQCard-5102 in any available Type II PCMCIA slot in your computer. For Windows 3.x, you must have Card and Socket Services 2.1 or later installed in your computer. If you have Windows 95, you should already have Card and Socket Services installed by the operating system.

The PC Card software configures the card for your computer and automatically assigns the base address. Before installing your DAQCard-5102, please consult your PC user manual or technical reference manual for specific instructions and warnings. Use the following general instructions to install your DAQCard-5102:

- 1. Turn off your computer. If your computer supports hot insertion, you may insert or remove the DAQCard-5102 at any time, whether the computer is powered on or off.

- 2. Remove the PCMCIA slot cover on your computer.

- 3. Insert the 68-pin I/O connector of the DAQCard-5102 into the PCMCIA slot. The card is keyed so that you can insert it only one way.

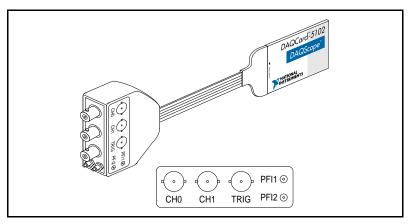

- 4. Attach the PSH32-C5 I/O cable, shown in Figure 4-3, to the PC Card to provide BNC connectivity. The cable connector latches into the DAQCard-5102. The other end of the cable assembly is a panel to which you can connect standard probes and cables. When plugging and unplugging the cable, always grasp the cable by the connector. Never pull directly on the cable to unplug it from the DAQCard-5102.

The DAQCard-5102 is now installed.

# **Hardware Configuration**

The DAQScope 5102 is a fully software-configurable, Plug and Play device. Configuration information is stored in nonvolatile memory. The Plug and Play services query the device, read the information, and arbitrate resource allocation for items such as base address, interrupt level, and DMA channel. After assigning these resources, the operating system enables the device for operation.

# **Digitizer Basics**

This chapter explains basic information you need to understand about making measurements with digitizers, including important terminology and using your probe.

# **Understanding Digitizers**

To understand how digitizers work, you should be familiar with the Nyquist theorem and how it affects analog bandwidth and sample rate. You should also understand terms including vertical sensitivity, analog-to-digital converter (ADC) resolution, record length, and triggering options.

### **Nyquist Theorem**

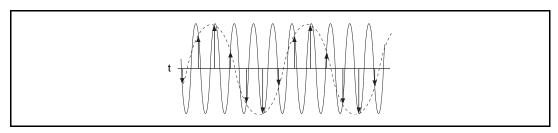

The Nyquist theorem states that a signal must be sampled at least twice as fast as the bandwidth of the signal to accurately reconstruct the waveform; otherwise, the high-frequency content will *alias* at a frequency inside the spectrum of interest (passband). An alias is a false lower frequency component that appears in sampled data acquired at too low a sampling rate. Figure 3-1 shows a 5 MHz sine wave digitized by a 6 MS/s ADC. The dotted line indicates the aliased signal recorded by the ADC at that sample rate.

**Figure 3-1.** Sine Wave Demonstrating the Nyquist Frequency

The 5 MHz frequency aliases back in the passband, falsely appearing as if it were a 1 MHz sine wave. To prevent aliasing in the passband, a lowpass filter limits the frequency content of the input signal above the Nyquist rate.

### **Analog Bandwidth**

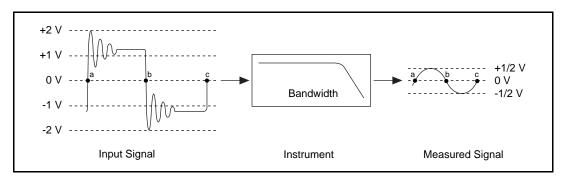

Analog bandwidth describes the frequency range (in Hertz) in which a signal can be digitized accurately. This limitation is determined by the inherent frequency response of the input path—from the tip of the probe to the input of the ADC—which causes loss of amplitude and phase information. Analog bandwidth is the frequency at which the measured amplitude is 3 dB below the actual amplitude of the signal. This amplitude loss occurs at very low frequencies if the signal is AC coupled and at very high frequencies regardless of coupling. When the signal is DC coupled, the bandwidth of the amplifier will extend all the way to the DC voltage. Figure 3-2 illustrates the effect of analog bandwidth on a high-frequency signal. The result is a loss of high-frequency components and amplitude in the original signal as the signal passes through the instrument.

Figure 3-2. Analog Bandwidth

### Sample Rate

Sample rate is the rate at which a signal is sampled and digitized by an ADC. According to the Nyquist theorem, a higher sample rate produces accurate measurement of higher frequency signals if the analog bandwidth is wide enough to let the signal to pass through without attenuation. A higher sample rate also captures more waveform details.

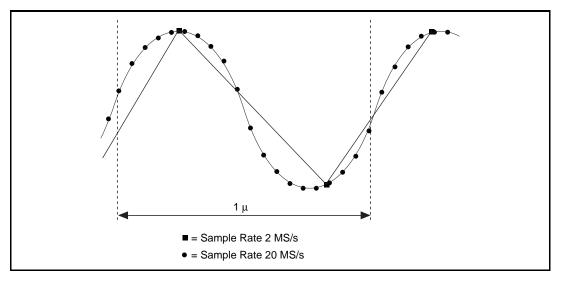

Figure 3-3 illustrates a 1 MHz sine wave sampled by a 2 MS/s ADC and a 20 MS/s ADC. The faster ADC digitizes 20 points per cycle of the input signal compared with 2 points per cycle with the slower ADC. In this example, the higher sample rate more accurately captures the waveform shape as well as frequency.

Figure 3-3. 1 MHz Sine Wave Sample

### **Vertical Sensitivity**

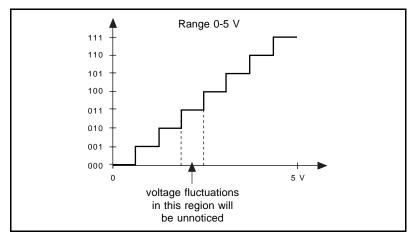

Vertical sensitivity describes the smallest input voltage change the digitizer can capture. This limitation is because one distinct digital voltage encompasses a range of analog voltages. Therefore, it is possible that a minute change in voltage at the input is not noticeable at the output of the ADC. This parameter depends on the input range, gain of the input amplifier, and ADC resolution. It is specified in volts per LSB. Figure 3-4 shows the transfer function of a 3-bit ADC with a vertical range of 5 V having a vertical sensitivity of 5/8 V/LSB.

Figure 3-4. Transfer Function of a 3-Bit ADC

### **ADC** Resolution

*ADC resolution* limits the accuracy of a measurement. The higher the resolution (number of bits), the more accurate the measurement. An 8-bit ADC divides the vertical range of the input amplifier into 256 discrete levels. With a vertical range of 10 V, the 8-bit ADC cannot resolve voltage differences smaller than 39 mV. In comparison, a 12-bit ADC with 4,096 discrete levels can resolve voltage differences as small as 2.4 mV.

### **Record Length**

Record length refers to the amount of memory dedicated to storing digitized samples for postprocessing or display. In a digitizer, record length limits the maximum duration of a single-shot acquisition. For example, with a 1,000-sample buffer and a sample rate of 20 MHz, the duration of acquisition is 50 μs (the number of points multiplied by the acquisition time/point or 1,000 x 50 ns). With a 100,000-sample buffer and a sample rate of 20 MHz, the duration of acquisition is 5 ms (100,000 x 50 ns). The DAQScope 5102 has a buffer size of 663,000 samples. When performing a single-channel acquisition, you can use the entire available memory to capture data for a duration of 33.1 ms at 20 MS/s.

The DAQScope PCI-5102 record length for single-shot acquisitions is limited by the amount of memory available in your computer, because the data transfer rate on the PCI bus is higher than the acquisition rate on the DAQScope 5102 devices.

### **Triggering Options**

One of the biggest challenges of making a measurement is to successfully trigger the signal acquisition at the point of interest. Since most high-speed digitizers actually record the signal for a fraction of the total time, they can easily miss a signal anomaly if the trigger point is set incorrectly. The DAQScope 5102 is equipped with sophisticated triggering options, such as trigger thresholds, programmable hysteresis values, trigger hold-off, and bilevel triggering on input channels as well as on a dedicated trigger channel. The DAQScope 5102 also has two digital triggers that give you more flexibility in triggering by allowing you to connect a TTL/CMOS digital signal to trigger the acquisition. See Chapter 4, *Hardware Overview*, for more information on triggering.

# **Making Accurate Measurements**

For accurate measurements, you should use the right settings when acquiring data with your DAQScope 5102. Knowing the characteristics of the signal in consideration helps you to choose the correct settings. Such characteristics include:

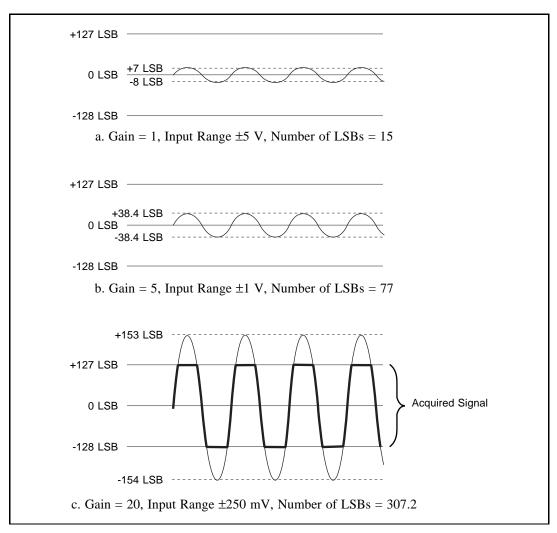

• Peak-to-peak value—This parameter, in units of volts, reflects the maximum change in signal voltage. If V is the signal voltage at any given time, then V<sub>pk-to-pk</sub> = V<sub>max</sub>-V<sub>min</sub>. The peak-to-peak value affects the vertical sensitivity or gain of the input amplifier. If you do not know the peak-to-peak value, start with the smallest gain (maximum input range) and increase it until the waveform is digitized using the maximum dynamic range without clipping the signal. Refer to Appendix A, Specifications, for the maximum input voltage for your DAQScope 5102 device. Figure 3-5 shows that a gain of 5 is the best setting to digitize a 300 mV, 1 MHz sine wave without clipping the signal.

Figure 3-5. Dynamic Range of an 8-Bit ADC with Three Different Gain Settings

Source impedance—Most digitizers and digital storage oscilloscopes (DSOs) have a 1 MΩ input resistance in the passband with a 1X probe and a 10 MΩ input resistance with a 10X probe. If the source impedance is large, the signal will be attenuated at the amplifier input and the measurement will be inaccurate. If the source impedance is unknown but suspected to be high, change the attenuation ratio on your probe and acquire data. If the 10X measurement results in amplitude gain, your measurement may be inaccurate. To correct this, try reducing the source impedance by buffering. See *Understanding the Probe and Its Effects on Your Waveform* later in this chapter for more information.

In addition to the input resistance, all digitizers, DSOs, and probes present some input capacitance in parallel with the resistance. This capacitance can interfere with your measurement in much the same way as the resistance does. You can reduce this capacitance by using an attenuating probe (10X or 100X) or an active probe. See Appendix A, *Specifications*, or your probe specifications for accurate input capacitance numbers.

- Input frequency—If your sample rate is less than twice the highest frequency component at the input, the frequency components above half your sample rate will alias in the passband at lower frequencies, indistinguishable from other frequencies in the passband. If the signal's highest frequency is unknown, you should start with the digitizer's maximum sample rate to prevent aliasing and reduce the digitizer's sample rate until the display shows either enough cycles of the waveform or the information you need.

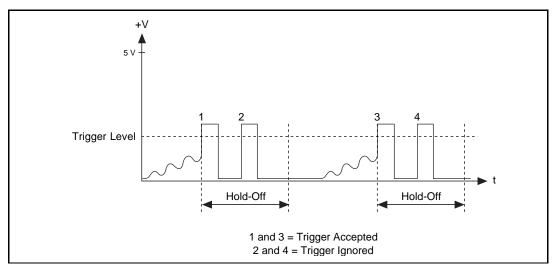

- General signal shape—Some signals are easy to capture by ordinary triggering methods. A few iterations on the trigger level finally render a steady display. This method works for sinusoidal, triangular, square, and saw tooth waves. Some of the more elusive waveforms, such as irregular pulse trains, runt pulses, and transients, may be more difficult to capture. Figure 3-6 shows an example of a difficult pulse-train trigger.

Figure 3-6. Difficult Pulse Train Signal

Ideally, the trigger event should occur at condition one, but sometimes the instrument may trigger on condition two because the signal crosses the trigger level. You can solve this problem without using complicated signal processing techniques by using *trigger hold-off*, which lets you specify a time from the trigger event to ignore additional triggers that fall within that time. With an appropriate hold-off value, the waveform in Figure 3-6 can be properly captured by discarding conditions two and four.

• Input coupling—You can configure the input channels on your DAQScope 5102 to be DC coupled or AC coupled. DC coupling allows DC and low-frequency components of a signal to pass through without attenuation. In contrast, AC coupling removes DC offsets and attenuates low frequency components of a signal. This feature can be exploited to zoom in on AC signals with large DC offsets, such as switching noise on a 12 V power supply. Refer to Appendix A, *Specifications*, for input limits that must be observed regardless of coupling.

# Understanding the Probe and Its Effects on Your Waveform

Signals travel from the tip of the probe to the input amplifier and then are then digitized by the ADC. This signal path makes the probe an important electrical system component that can severely affect the accuracy of the measurement. A probe can potentially influence measured amplitude and phase, and the signal can pick up additional noise on its way to the input stage. Several types of probes are available including passive, active, and current probes.

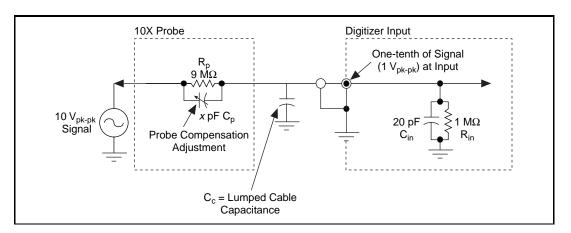

### The Passive Probe

The passive probe is the most widely used general-purpose oscilloscope probe. Passive probes are specified by bandwidth (or rise time), attenuation ratio, compensation range, and mechanical design aspects. Probes with attenuation, 10X or 100X, have a tunable capacitor that can reduce capacitive effects at the input. The ability to cancel or minimize effective capacitance improves the probe's bandwidth and rise time. Figure 3-7 shows a typical 10X probe model. You should adjust the tunable capacitor,  $C_p$ , to obtain a flat frequency response.  $C_p$  is the probe capacitance,  $R_p$  is the probe resistance,  $C_{in}$  is the input capacitance,  $C_{in}$  is the input resistance.

Figure 3-7. Typical 10X Probe

Analytically, obtaining a flat frequency response means:

$$R_{in}/(R_{in} + R_p) = C_p/(C_p + C_{in} + C_c)$$

It can be shown that:

$$R_{in}(C_{in} + C_c) = C_p R_p;$$

or the time constant of the probe equals the time constant of the digitizer input.

### **How to Compensate Your Probe**

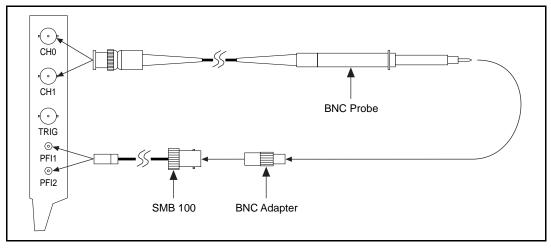

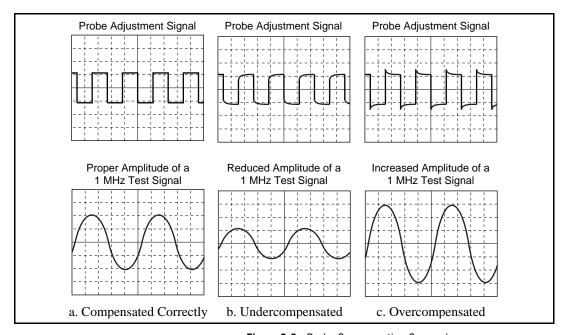

Adjusting the tunable probe capacitor to get a flat frequency response is called *probe compensation*. On the DAQScope 5102, you can select a 0–5 V, 1 kHz pulse train as reference to output on PFI1 or PFI2. Refer to Figure 3-8 as you follow these instructions to compensate your probe:

- Connect the BNC end of the probe to an input channel, either CH0 or CH1.

- 2. Attach the BNC adapter (probe accessory) to the tip of the probe.

- Connect the SMB100 probe-compensation cable to one of the PFI lines.

- 4. Attach the probe with the BNC adapter to the BNC female end of the SMB100 cable.

- 5. Enable the probe compensation signal on the PFI line you selected in step 3. See your application software documentation for more information how to perform this step.

- 6. Digitize data on the input channel.

- 7. Adjust the tunable capacitor to make the waveform look as square as possible.

Figure 3-8. Connecting the Probe Compensation Cabling

As shown in Figure 3-8, an undercompensated probe attenuates higher frequency signals, whereas an overcompensated probe amplifies higher frequencies. Calibrate your probe frequently to ensure accurate measurements from your DAQScope 5102.

**Figure 3-9.** Probe Compensation Comparison

### **Active and Current Probes**

You can also use active probes and current probes with digitizers and DSOs.

Active probes such as differential and field-effect transistor (FET) probes contain active circuitry in the probe itself to reject noise and amplify the signal. FET probes are useful for low-voltage measurements at high frequencies and differential probes are noted for their high CMRR and nongrounded reference.

Instead of using a series resistance in the loop to measure current, current probes measure AC and/or DC current flowing in a conductor magnetically. This lack of series resistance causes very little interference in the circuit being tested.

# **Hardware Overview**

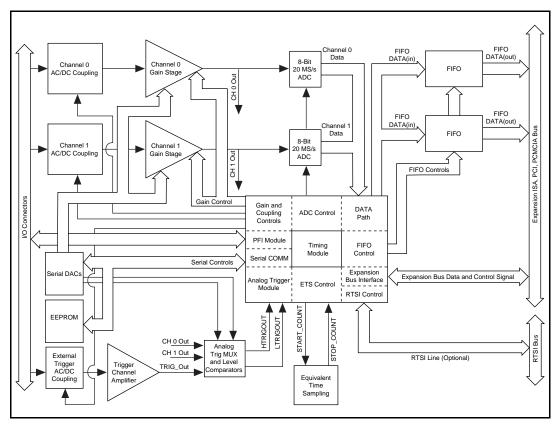

This chapter includes an overview of the DAQScope 5102, explains the operation of each functional unit making up your DAQScope 5102, and describes the signal connections.

Figure 4-1 shows a block diagram of the DAQScope 5102.

Figure 4-1. DAQScope 5102 Block Diagram

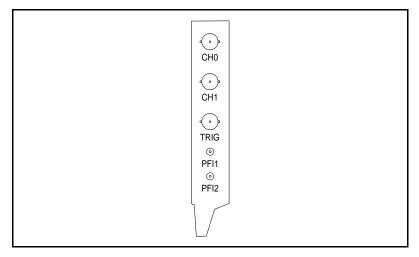

# I/O Connector

The DAQScope 5102 devices have two standard BNC female connectors for CH0 and CH1 analog input connections, one standard BNC female connector for the TRIG channel, and two standard SMB female connectors for the multipurpose digital timing and triggering signals, PFI1 and PFI2. The PCI-5102 and AT-5102 give you direct BNC connectivity on the bracket, as shown in Figure 4-2.

Figure 4-2. AT-5102 and PCI-5102 Connectors

Use the cable assembly provided for these connections on the DAQCard-5102, as shown in Figure 4-3.

Figure 4-3. DAQCard-5102 Connector

# **Signal Connections**

Table 4-1. I/O Connector Signal Descriptions

| Signal     | Description                                               |  |  |

|------------|-----------------------------------------------------------|--|--|

| CH0, CH1   | Digitizes data and triggers acquisitions                  |  |  |

| TRIG       | Used for external analog triggering                       |  |  |

| PFI1, PFI2 | Software-configurable digital triggers or digital outputs |  |  |

You can use CH0 and CH1 to digitize data as well as to trigger an acquisition. Use the TRIG channel for an external analog trigger only; data on the TRIG channel cannot be digitized. PFI1 and PFI2 are digital signals that you can use for timing-critical applications. When used as inputs, PFI lines can trigger an acquisition and/or allow an external scan clock connection. In the output mode, PFI lines can output Start Trigger, Stop Trigger, Scan Clock, and End of Acquisition signals as well as analog trigger circuit output (ATC\_OUT), frequency output, and TTL low and high voltage information. Signal names and descriptions vary depending on the acquisition mode you are using. See the *Acquisition Modes* section later in this chapter for more information on timing and triggering.

## **Analog Input**

The two analog input channels are referenced to common ground in bipolar mode. These settings are fixed; therefore, neither the reference nor the polarity of input channels can be changed. You cannot use CH0 or CH1 to make differential measurements or measure floating signals, unless you subtract the digital waveforms in software. For accurate measurements, make sure the signal being measured is referenced to the same ground as your DAQScope 5102 by attaching the probe's ground clip to the signal ground. Table 4-2 shows the input ranges available on CH0 and CH1.

| Gain | Input range            |           |            |  |

|------|------------------------|-----------|------------|--|

|      | 1X Probe               | 10X Probe | 100X Probe |  |

| 1    | ±5 V (default setting) | ±50 V     | ±500 V     |  |

| 5    | ±1 V                   | ±10 V     | ±100 V     |  |

| 20   | ±0.25 V                | ±2.5 V    | ±25 V      |  |

| 100  | ±50 mV                 | ±0.5 V    | ±5 V       |  |

Table 4-2. CHO and CH1 Input Ranges

Note:

The 10X and 100X designations mean divide-by, not amplify. For example, with a 100X probe and a gain of 1, if you measure a 400 V signal, the DAQScope 5102 will receive 4 V (400 V/100 = 4 V) at its input connector.

The TRIG channel has a fixed input range of  $\pm 5$  V. All DAQScope 5102 devices power up with a default gain of 1, thereby allowing the largest input range available. TRIG channel range values are the same as the gain of 1 values in Table 4-2.

The CH0, CH1, and TRIG channels have a software-programmable coupling selection between AC and DC. Use AC coupling when your AC signal contains a large DC component. Without AC coupling, it is difficult to view details of the AC component with a large DC offset and a small AC component, such as switching noise on a DC supply. If you enable AC coupling, you remove the large DC offset for the input amplifier and amplify only the AC component. This technique makes effective use of dynamic range to digitize the signal of interest. The *low frequency corner* in an AC-coupled circuit is the frequency below

which signals are attenuated by at least 3 dB. The low frequency corner is 11 Hz with a 1X probe, 1.1 Hz with a 10X probe, and 0.11 Hz with a 100X probe.

When changing coupling on the DAQScope 5102 devices, the input stage takes a finite time to settle, as shown in Table 4-3.

| Table 4-3. | AC/DC | Coupling | Change | Settling | Rates |

|------------|-------|----------|--------|----------|-------|

|------------|-------|----------|--------|----------|-------|

| Action                                                                                                            | Settling Time            |

|-------------------------------------------------------------------------------------------------------------------|--------------------------|

| Switching from AC coupling to DC coupling                                                                         | 0.5 ms                   |

| Switching from DC coupling to AC coupling 1X probe time constant 10X probe time constant 100X probe time constant | 15 ms<br>150 ms<br>1.5 s |

Warning: When switching coupling from DC to AC, returned data is accurate about 20 time constants after switching to AC. This delay is based on switching to AC and, at the same time, switching from a gain of 1 to a gain of 100. NI-DAQ does not provide the delay to account for settling time; therefore, acquisitions immediately following a coupling change may yield incorrect data.

### **ADC Pipeline Delay**

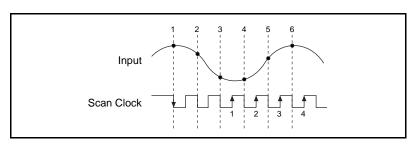

The ADC on the DAQScope 5102 is a pipelined flash converter with a maximum conversion rate of 20 MS/s. The pipelined architecture imposes a 2.5 Scan Clock cycle delay to convert analog voltage into a digital value, as shown in Figure 4-4.

Figure 4-4. Scan Clock Delay

In reference to the Scan Clock signal, the digital value corresponding to the first conversion (the first falling edge of the Scan Clock signal) outputs synchronously with the third rising edge of the Scan Clock signal.

Using pipelined architecture also introduces a lower limit on the scan rate. For the DAQScope 5102, the accuracy starts to degrade below about 1 kS/s.

The DAQScope 5102 is designed to automatically adjust for pipelined delay when you use the internal scan clock. If you use an external scan clock, you must provide a free-running clock to ensure reliable operation. You must also follow timing specifications on the external scan clock as described in Appendix A, *Specifications*.

#### **Acquisition Modes**

The DAQScope 5102 supports two acquisition modes—posttrigger acquisition and pretrigger acquisition.

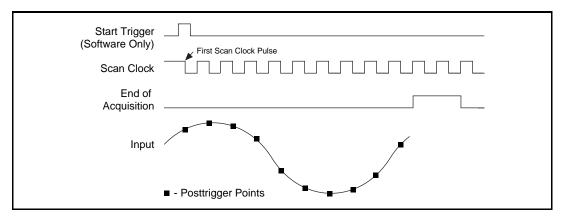

#### **Posttrigger Acquisition**

In posttrigger acquisition mode, the hardware acquires a number of scans after the Start Trigger occurs. When the trigger occurs, the input signal is digitized and the desired number of scans are stored in onboard memory. Table 4-4 shows the minimum and maximum number of samples the 5102 device can acquire.

| Number of<br>Channels           | PCI-5102 |             | PCI-5102 |         |  | 102 and<br>ard-5102 |

|---------------------------------|----------|-------------|----------|---------|--|---------------------|

|                                 | Min Max  |             | Min      | Max     |  |                     |

| One                             | 360      | 16,777,088* | 360      | 663,000 |  |                     |

| Two                             | 180      | 16,777,088* | 180      | 331,500 |  |                     |

| * Dependent on available memory |          |             |          |         |  |                     |

**Table 4-4.** Possible Number of Samples for Posttriggered Scans

Chapter 4

#### Note:

If Scan Clock is internally generated, NI-DAQ hides the minimum posttriggered scan count hardware restriction by acquiring the minimum number of points and discarding the unwanted points. If Scan Clock is internally supplied, you do not need to do anything. If Scan Clock is externally supplied, you must supply a free-running clock for proper operation.

On the AT-5102 and the DAQCard-5102, data transfer takes place after an acquisition ends, limiting the scan count to the size of the onboard memory.

On the PCI-5102, data can be moved very quickly from the card to host memory while an acquisition is in progress. The PCI-5102 takes advantage of the National Instruments MITE Application-Specific Integrated Circuit (ASIC) to master the PCI bus and transfer data acquired on both channels to PC memory in real time without losing data. This technology lets you acquire more data than 663,000 samples, the size of the onboard memory. This property of the PCI bus extends the maximum scan count to 16 million scans.

Figure 4-5 shows the timing signals involved in a posttrigger acquisition. In this example, the hardware is programmed to acquire 10 posttriggered scans. Posttrigger acquisition mode is used only for one-shot software-triggered acquisitions.

Figure 4-5. Posttrigger Acquisition

Table 4-5 describes the posttrigger acquisition signals.

**Table 4-5.** Posttrigger Acquisition Signals

| Signal             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Start Trigger      | Triggers the acquisition. It can be generated through software, or CH0, CH1, TRIG, PFI1, and PFI2, or any of the seven RTSI bus trigger lines. RTSI bus trigger lines are available only on the PCI-5102 and AT-5102.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Scan Clock         | Causes the ADC to convert the input signal into digital data. This signal is also used in the memory controller to write the data into onboard memory. This signal can be generated internally, with a 24-bit counter clocked with a 20 MHz signal to generate pulses from 20 MHz to 1.19 Hz. The 24-bit counter provides a wide choice of valid frequencies for the Scan Clock signal. In addition, Scan Clock can also be selected from CH0, CH1, TRIG, PFI1, and PFI2, or any of the seven RTSI bus trigger lines. RTSI bus trigger lines are available only on the PCI-5102 and AT-5102. |  |  |

| End of Acquisition | Indicates end of acquisition to the control logic in the hardware. It is generated from a counter that keeps track of the number of points remaining in the acquisition. It can be exported from the device on the PFI lines.                                                                                                                                                                                                                                                                                                                                                                |  |  |

#### **Pretrigger Acquisition**

In pretrigger acquisition mode, the device acquires a certain number of scans, called the pretrigger scan count, *before* the trigger occurs. After satisfying the pretrigger scan count requirement, hardware keeps acquiring data and stores it in a circular buffer implemented in onboard memory. The size of the circular buffer equals the pretrigger scan count. When the trigger occurs, hardware acquires and stores the posttrigger scan count and the acquisition terminates. Table 4-6 shows the minimum and maximum number of samples available on the DAQScope 5102 in pretriggered mode.

Table 4-6.

Possible Number of Samples for Pretriggered Scans

| Number of Channels              | PCI-5102 |             | AT-5102 and DAQCard-510 |                                              |  |

|---------------------------------|----------|-------------|-------------------------|----------------------------------------------|--|

|                                 | Min      | Max         | Min                     | Max                                          |  |

| One                             |          |             |                         |                                              |  |

| Pretriggered scans              | 360      | 663,000     | 360                     | 663,000 - (the number of                     |  |

|                                 |          |             |                         | posttriggered scans)                         |  |

| Posttriggered scans             | 10       | 16,777,088* | 10                      | 663,000 - (the number of pretriggered scans) |  |

| Two                             |          |             |                         |                                              |  |

| Pretriggered scans              | 180      | 331,500     | 180                     | 331,500 - (the number of                     |  |

|                                 |          |             |                         | posttriggered scans)                         |  |

| Posttriggered scans             | 5        | 16,777,088* | 5                       | 331,500 - (the number of pretriggered scans) |  |

| * Dependent on available memory |          |             |                         |                                              |  |

#### Note:

If Scan Clock is internally generated, NI-DAQ hides the minimum pretriggered scan count hardware restriction by acquiring the minimum number of points and discarding the unwanted points. If Scan Clock is externally supplied, a free-running clock must be used for proper operation.

Figure 4-6 shows the relevant timing signals for a typical pretriggered acquisition. The illustration represents five pretrigger and five posttrigger scans, and above-high-level analog triggering is used. See the *Analog Trigger Circuit* section later in this chapter for more information on analog trigger types.

Figure 4-6. Pretrigger Acquisition

Table 4-7. Pretrigger Acquisition Signals

| Signal             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start Trigger      | Starts data acquisition. In pretrigger mode, the Start Trigger signal enables the storage of pretrigger data. Start Trigger can only be generated through software in pretrigger mode.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Scan Clock         | Causes the ADC to convert the input signal into digital data. This signal is also used in the memory controller to write the data into onboard memory. This signal can be generated internally, with a 24-bit down counter clocked with a 20 MHz signal to generate pulses from 20 MHz to 1.19 Hz. The 24-bit counter provides a wide choice of valid frequencies for the Scan Clock signal. In addition, Scan Clock can also be selected from CH0, CH1, TRIG, PFI1, and PFI2, or any of the seven RTSI bus trigger lines. RTSI bus trigger lines are available only on the PCI-5102 and AT-5102. |

| SC_TC              | Scan counter terminal count (SC_TC) is an internally generated signal that pulses once to indicate that the pretrigger sample count requirement is met. Between the time when this signal pulses and the Stop Trigger occurs, hardware overwrites the oldest points in memory with the most recent points in a circular fashion. All STOP triggers occurring before SC_TC are ignored by the device.                                                                                                                                                                                              |

| Stop Trigger       | Terminates the acquisition sequence after acquiring the posttrigger sample count. This trigger can be generated through software, or CH0, CH1, TRIG, PFI1, and PFI2, or any of the seven RTSI bus trigger lines. RTSI bus trigger lines are available only on the PCI-5102 and AT-5102.                                                                                                                                                                                                                                                                                                           |

| End of Acquisition | Indicates end of acquisition to the control logic in the hardware. It is generated from a counter that keeps track of points remaining to acquire. It can be exported from the device on the PFI lines.                                                                                                                                                                                                                                                                                                                                                                                           |

#### **Trigger Sources**

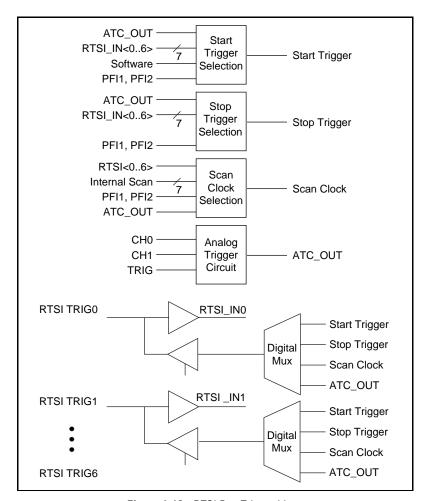

The Scan Clock, Start Trigger, and Stop Trigger signals can be generated through software or supplied externally as digital triggers or as analog triggers on one of the input channels or the TRIG channel. Figure 4-7 shows the different trigger sources. In addition, Scan Clock is available from a source (counter) internal to the DAQScope 5102.

Figure 4-7. Scan Clock, Start Trigger, and Stop Trigger Signal Sources

#### **Analog Trigger Circuit**

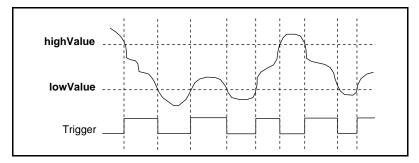

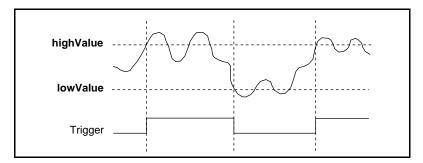

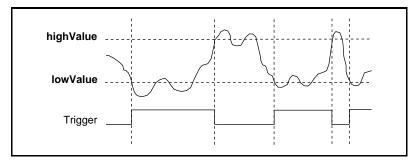

The DAQScope 5102 contains a sophisticated analog trigger circuit that accepts Boolean outputs from level comparators and makes intelligent decisions about the trigger. Five analog triggering modes are available, as shown in Figures 4-8 through 4-12. You can set **lowValue** and **highValue** independently in software.

In below-low-level analog triggering mode, the trigger is generated when the signal value is less than **lowValue**. **HighValue** is unused.

Figure 4-8. Below-Low-Level Analog Triggering Mode

In above-high-level analog triggering mode, the trigger is generated when the signal value is greater than **highValue**. **LowValue** is unused.

Figure 4-9. Above-High-Level Analog Triggering Mode

In inside-region analog triggering mode, the trigger is generated when the signal value is between the **lowValue** and the **highValue**.

Figure 4-10. Inside-Region Analog Triggering Mode

In high-hysteresis analog triggering mode, the trigger is generated when the signal value is greater than **highValue**, with hysteresis specified by **lowValue**.

Figure 4-11. High-Hysteresis Analog Triggering Mode

In low-hysteresis analog triggering mode, the trigger is generated when the signal value is less than **lowValue**, with hysteresis specified by **highValue**.

Figure 4-12. Low-Hysteresis Analog Triggering Mode

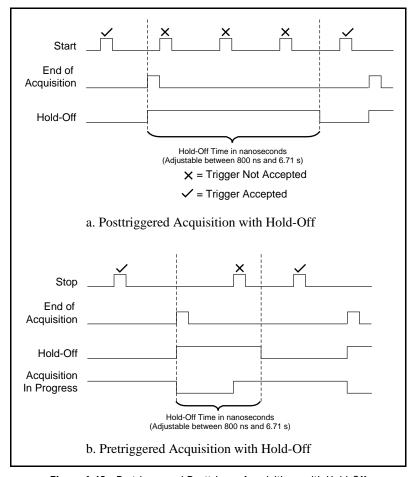

#### **Trigger Hold-Off**

Trigger hold-off is provided in hardware using a 24-bit down counter clocked by a 2.5 MHz internal timebase. With this configuration, you can select a hardware hold-off value of 800 ns to 6.71 s in increments of 400 ns.

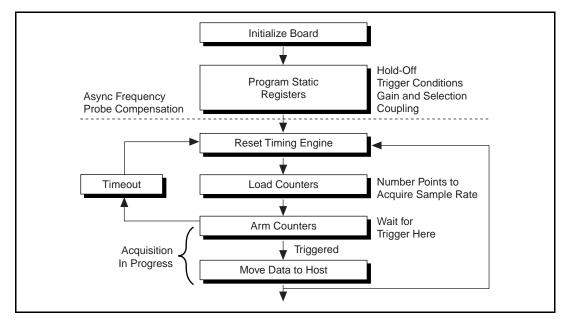

When acquisition is in progress, the counter is loaded with a digital value that corresponds to the desired hold-off time. The End of Acquisition signal triggers the counter to start counting down. Before the counter reaches its terminal count (TC), all triggers are rejected in hardware. At TC, the hold-off counter reloads the hold-off value and waits for the End of Acquisition to repeat the process. Figure 4-13 shows a timing diagram of signals when hold-off is enabled.

Figure 4-13. Pretrigger and Posttrigger Acquisitions with Hold-Off

Note:

When you use trigger hold-off, you cannot calibrate your probe or generate an asynchronous frequency at the same time. The counter that generates hold-off also generates the probe calibration signal and the asynchronous pulse train.

### Random Interleaved Sampling

Random Interleaved Sampling (RIS) is a form of Equivalent Time Sampling (ETS) that allows acquisition of pretriggered data. ETS refers to any method used to sample signals in such a way that the apparent sampling rate is higher than the real sampling rate. ETS is accomplished by sampling different points along the waveform for each occurrence of the trigger, and then reconstructing the waveform from the data acquired over many cycles.

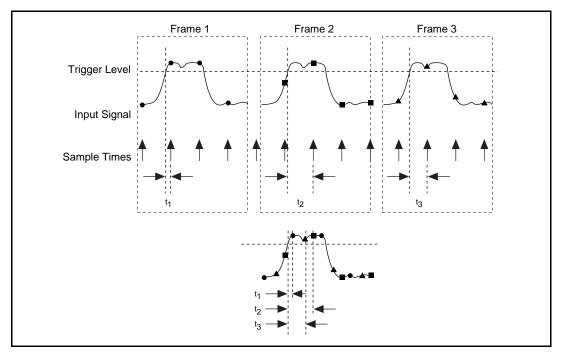

In RIS, the arrival of the waveform trigger point occurs at some time randomly distributed between two sampling instants. The time from the trigger to the next sampling instant is measured, and this measurement allows the waveform to be reconstructed. Figure 4-14 shows three occurrences of a waveform. In Frame 1, the dotted points are sampled, and the trigger occurs time  $t_1$  before the next sample. In Frame 2, the square points are sampled, and the trigger occurs time  $t_2$  before the next sample. In Frame 3, the triangular points are sampled, and the trigger occurs time  $t_3$  before the next sample. With knowledge of the three times,  $t_1$ ,  $t_2$ , and  $t_3$ , you can reconstruct the waveform as if it had been sampled at a higher rate, as shown at the bottom of the figure.

Figure 4-14. Waveform Reconstruction with RIS

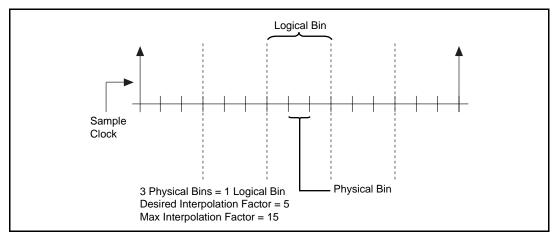

The time measurement is made with a time-to-digital converter (TDC). The resolution of the TDC is the number of physical bins to which the TDC can quantize the trigger arrival time. This resolution should be several times higher than the maximum desired interpolation factor, which is the maximum number of logical bins to which you want the trigger arrival time quantized. The higher resolution ensures that when the TDC output is requantized to the desired interpolation factor, all output values have a roughly equal probability of occurrence; that is, all logical bins will contain approximately the same number of physical bins.

For example, consider the maximum interpolation factor to be 5. If the TDC could output values from 0 to 15, then each logical bin will contain three physical bins, as shown in Figure 4-15.

**Figure 4-15.** Relationship between Interpolation Factor, Logical Bins, and Physical Bins

The maximum interpolation factor on the DAQScope 5102 is 50, resulting in a maximum ETS rate of 1 GS/s. At this rate, the ratio of logical bins to physical bins is approximately 1:9.

To reconstruct the waveform with RIS, you need to know the RIS OFFSET, which is the minimum value that the TDC can return, and the range of values, RIS GAIN, which is the maximum TDC value minus the minimum TDC value.

RIS OFFSET and RIS GAIN may vary slightly from board to board. Both these parameters are computed individually for each board at the factory and the values are stored in the onboard EEPROM.

Use RIS GAIN to determine the number of physical bins per logical bin for the desired interpolation factor. You could use RIS OFFSET to start the waveform reconstruction at the origin, but this parameter may drift over time and temperature, which could result in an inaccurate waveform.

Note: ETS and RIS work only with repetitive signals.

#### **Calibration**

Calibration is the process of minimizing measurement errors by making small circuit adjustments. On the DAQScope 5102, NI-DAQ automatically makes these adjustments by retrieving precalculated values from the onboard EEPROM and writing them to calibration DACs (CalDACs).

All DAQScope 5102 devices are factory calibrated to the levels indicated in Appendix A, *Specifications*. Factory calibration involves nulling input offset, output offset, and gain errors on CH0 and CH1 and measuring RIS offset and RIS gain of the TDC, all at room temperature (25° C). These constants are stored in a write protected area in the EEPROM. Factory calibration may not be sufficient for some applications where different environmental conditions and the aging factor could induce inaccuracy. To recalibrate your DAQScope 5102, contact National Instruments.

### **RTSI Bus Trigger and Clock Lines**

◆ PCI-5102 and AT-5102

The RTSI bus (not available on the DAQCard-5102) allows National Instruments boards to synchronize timing and triggering on multiple devices. The RTSI bus has seven bidirectional trigger lines and one bidirectional clock signal.

You can program any of the seven trigger lines as inputs to provide Start Trigger, Stop Trigger, and Scan Clock signals sourced from a master board. Similarly, you can program a master board to output its internal Start Trigger, Stop Trigger, Scan Clock, and ATC\_OUT signals on any of the trigger lines, as shown in Figure 4-16.

Figure 4-16. RTSI Bus Trigger Lines

The RTSI bus clock line is a special clock line on the RTSI bus that can carry only the timebase of the master board to the slave board. For the smallest jitter between measurements on different boards, you should configure the slave devices to use the RTSI bus clock from the master device.

#### **PFI Lines**

All DAQScope 5102 devices have two multipurpose programmable function digital input/output lines, PFI1 and PFI2, that can be used for external timing and triggering or outputting various signals. The direction on these lines is individually selectable to be input or output.

#### **PFI Lines as Inputs**

PFI1 or PFI2 can be selected as inputs for the Start Trigger, Stop Trigger, and Scan Clock signals.

#### **PFI Lines as Outputs**

PFI1 or PFI2 can be selected to output the following digital signals:

- Start Trigger—This signal is synchronized to the 20 MHz timebase. When the Start condition is satisfied, either through a software, analog, or digital trigger, Start Trigger will transition high for 100 ns (two clock periods of the 20 MHz timebase) and transition back to its idle state.

- Stop Trigger—This signal is synchronized to the 20 MHz timebase.

When the Stop condition is satisfied, either through an analog or

digital trigger, Stop Trigger will transition high for 100 ns (two

clock periods of the 20 MHz timebase) and transition back to its

idle state.

- Scan Clock—This signal is also the clock to the ADC that represents the rate at which the input is sampled. The default state of this signal is high.

- End of Acquisition—This signal is generated internally to indicate to internal state machines that acquisition has ended. End of Acquisition, synchronous to Scan Clock, pulses high for two Scan Clock periods at the end of acquisition. This signal may be useful to trigger external circuits for timing critical applications.

- ATC\_OUT—This signal is the digital output of the Analog Trigger Circuit on the DAQScope 5102. The frequency and duty cycle of this signal depends on the trigger channel, the lowValue and highValue trigger levels, polarity, and triggering mode. For more information, see the *Analog Trigger Circuit* section earlier in this chapter.

- Frequency Output—This signal is a digital pulse train with programmable frequency. The most common application of Frequency Output for the DAQScope 5102 is to provide a signal for compensating the probe. You can select two timebases to generate this frequency as follows:

- 7.16 MHz (asynchronous to 20 MHz internal timebase)

- 1.25 MHz (synchronous to 20 MHz internal timebase)

The DAQScope 5102 uses a 16-bit counter to programmatically select frequency at the output. The pulse train frequency as a function of counter value can be expressed as:

Frequency = timebase/divide\_ratio;

where,

divide ratio = 3 ... 65,535.

Alternatively, to compute divide\_ratio for a particular frequency, the relationship is:

divide\_ratio = timebase/frequency;

For example, to generate a 1 kHz pulse train, common for probe compensation, select the following parameters:

timebase = 1.25 MHz

divide ratio = 1,250

- Low—This is TTL low voltage referenced to the computer's ground potential. This is a signal at logic level low. Do not use this as GND for your circuit.

- High—This is TTL high voltage referenced to the computer's ground potential. This is a signal at logic level high. Do not use this as VCC for your circuit.

Warning: Refer to the output drive specification of PFI lines in Appendix A, Specifications. Failure to observe these limits may severely damage your DAQScope 5102.

### **Master/Slave Operation**

You can use two or more DAQScope 5102 devices in one system to increase the number of channels for your application by synchronizing devices over the RTSI bus or through the I/O connector.

Use the RTSI bus for synchronizing two or more PCI-5102 and AT-5102 devices. For the DAQCard 5102, you must use the I/O connector.

#### Restrictions

To ensure proper master/slave operation on your 5102 device, you must observe the following restrictions:

- You must use all channels for acquisition. For example, if you want

to use three channels at a time, you cannot use two channels on the

master and one channel on the slave, you must use four channels for

data acquisition and discard data on the fourth channel.

- The desired pretrigger number of scans and total number of scans must be a multiple of four. This is a hardware limitation.

- There is a maximum of one sample clock timing jitter between master and slave cards.

#### **Connecting Devices**

♦ DAQCard-5102

You need two SMB200 cables (optional) and two DAQCard-5102 devices with cable assemblies to create a four-channel digitizer as follows:

- 1. Connect PFI1 of the master device to PFI1 of the slave device with the SMB200 cable.

- 2. Connect PFI2 of the master device to PFI2 of the slave device with the SMB200 cable.

- 3. Configure PFI1 of the master device to output Scan Clock and PFI2 of the master device to output Stop Trigger.

- 4. Configure the slave device to use external scans on PFI1, external Stop Trigger on PFI2, and software Start Trigger.

- 5. Refer to the *Determining Pretriggered and Posttriggered Scan Counts* section later in this chapter for information on how to configure the number of pretrigger and posttriggered scans for the master and the slave devices.

- Arm the slave device for acquisition before arming the master device.

You cannot use the PFI1 and PFI2 lines on master and slave devices for any other purpose when synchronizing two cards.

#### PCI-5102 and AT-5102

You can synchronize PCI-5102 and AT-5102 devices over the RTSI bus. You can configure a system where a PCI-5102 or AT-5102 can be the master device controlling a mix of PCI-5102 and AT-5102 slave devices. You need a RTSI bus cable (optional) to synchronize two or more 5102 devices over the RTSI bus as follows:

- Connect the master device with the slave device over the RTSI

connector. The cable and connector are keyed so there is only one

way to insert the cable in the connector.